�����������Դ����һ�����ο�˹�ض����и�����˵�����ο�˹�ض���ָ����ʱ�������ź�ת������ɢ�ź�ʱ����Ҫ��һ�������ڵIJ����������� 2 �Ρ�����������������������ָ���ʧ����Ϣ����ͼ 1 ���Ը������ؿ�����һ�㣬����ź�ÿ���ڲ���һ�Σ��õ���ֻ��һ��ֱ���ź�(����Ϊ����ֵ)����ͼ 1a ��ʾ�����ÿ���ڲ������Σ��õ�һ�������ź�(ͼ 1b)��ֵ��ע����ǣ��������źŽ���ÿ���� 2 �εIJ�����һ�ַdz������������κ�ʱ��Ҫ�������������ͼ 1c ��ʾ���� 200kHz �����ʶ� 190kHz �źŽ��в���������������ź���һ����õ����Ҳ�����Ƶ���Ǵ���ġ�Ƶ�ʵĸı��������ڻ�������µġ�

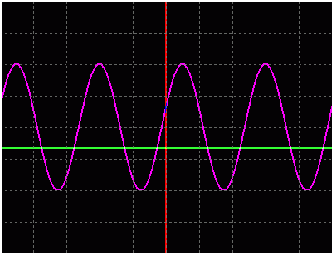

ͼ 1a. �������źŽ���ÿ����һ�εIJ���ʱ���õ�һ������Ϊ����ֵ��ֱ���źš�

ͼ 1b. ��ͬһ���Ҳ�ÿ���ڲ������Σ��õ�һ��������������Ϣ��ʧ��

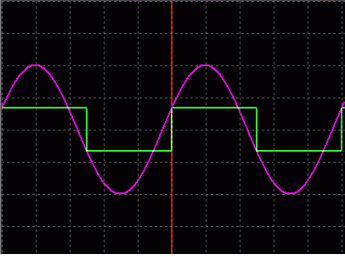

ͼ 1c. Fsignal = 190kHz��Fs = 200kHz ��Ƿ�����źţ����ý���ǻ�������µġ�

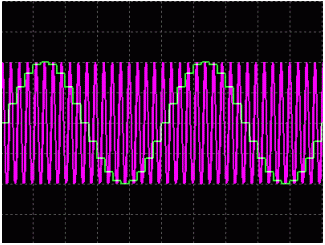

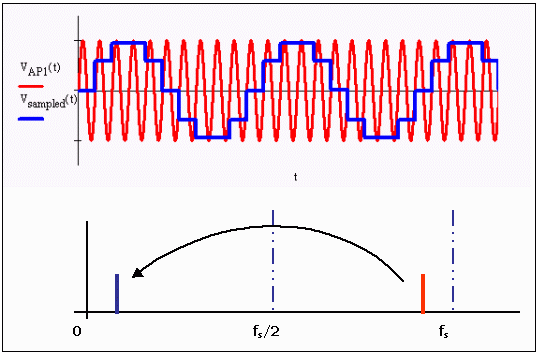

ͼ 2 ��ʾ����Ƶ��ı�����ʽ����ͼ�п��Կ�����Ƶ�ʸ��� f �� fs/2 ���źű����� fs/2��Ϊ�˱������������뱣֤�ź���û�и��ߵ�Ƶ�ʳɷݡ���ˣ����DZ����˽��źŵ����Ƶ�ʣ�����Ƶ����Ҫ�������Ƶ�ʵ�������һ����ԭʼ�Ŀ����Ǵ���������������⣬������Ȼ�Dz���ȡ�ģ���Ϊһ������źŲ�������Щ�źŻ����������Ȥ��Ƶ�Σ��������ź����Ƴ���ЩƵ�ʳɷݡ�������˲�������ģ������У������źŲ���֮ǰ��

ͼ 2. Ƶ���еĻ������Ƿ�����źž��� fs/2��

��һ�� �� ��ƿ�����˲�������ƿ�����˲�����Ҫ����ȷ����ϣ�����˲�����(��ֹƵ�ʡ����ɴ�˥����)��Ȼ��ѡ���ܹ�����Ӧ�����������˲�����(��ʱ��Ϊ�˲�������)��һ������£����ù����������ҹ�����Ƶ��Խ�ߣ��˲������Խ���ס����ǣ���������Ҫ�������ʵ� ADC���ɱ�ҲԽ�ߡ�

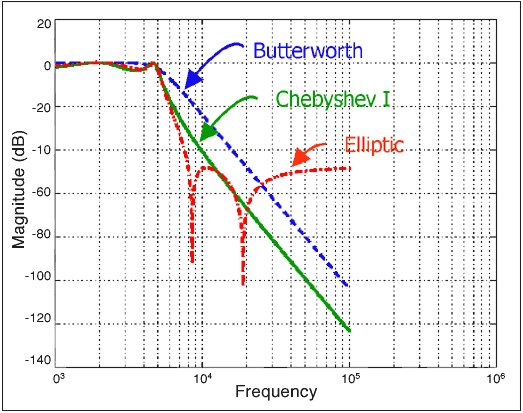

���磬����������Ϊ 8 ʱ������Ƶ��������ź�Ƶ�ʵİ˱������� ADC �ɱ����˲������Ӷȷ���ﵽ��һ���Ϻõ����ԡ����� ADC �ֱ���Ϊ 14 λ���ܹ��ṩ 80dB �������(SNR)������һ��IJ�����(����Ϊ�ź�Ƶ�ʵ� 4 ��)ʱ����ͨ�˲�����Ҫ�ṩ 80dB ��˥������ȷ��������ɢ�źž����㹻��˥������������ڲ�������ź��С�����ζ���ڹ��ɴ�����Ҫ�ṩÿ��Ƶ�� 40dB ��˥������Ҫ�߽��˲����ﵽ��һ���Ҫ��7 �װ�����˹�˲����ܹ���������Ҫ�����ھ���Ӧ�ò������ѡ����Բ�ͬ��Ӧ��ѡ��ͬ���˲������ͣ�ͼ 3 ��ʾΪ������˹�˲������б�ѩ���˲�������Բ�˲�����Ƶ�����ԡ���ͼ�п��Կ��������Ǿ��в�ͬ��ͨ�������ɴ����ԡ���Բ�˲����������˹�˲�����ȣ���Բ�˲����Ĺ��ɴ������ͣ�������Ƶ���ԽϲӦ���ݾ���Ӧ��ѡ���˲������ͣ�������ͨ�����ݲɼ�ϵͳ������ѡ�ð�����˹�˲���(�������˲���)���������λ����Ҫ�ߵĻ���Ҳ����ѡ���б�ѩ��������Բ�˲�����

ͼ 3. ��ͬ�˲���Ƶ����Ӧ�ıȽ�

ͨ�õ� A/D ת�����У������е����ʵ� SAR (��αƽ�) ADC�����ڸ��ٵ��������ʵ����� ADC�����ڵ���ϵͳ�Ħ�-�� ADC�����Ƕ���Ҫ������˲��������˲�����Ҫ��ȡ����ת�����ʡ���ϣ�����������������-�� ADC �Ƚ����⡣����ת���������÷dz��ߵ���������ʺ�ת�����ʣ������������˲���������Ч�����ʣ����Ӱ��ֱ���(��̬��Χ)����ߡ���-�� ADC �Կ�����˲�����Ҫ������������ʺ�����ź�Ƶ��֮���йأ����ֶ�����Ľ���ͬ��Ҳ��������������������ת�����У���������¿���ѡ�ü� RC �˲�����ѡ�ýϼĿ�����˲���������ϳ��Ĵ�����ʱ����Ϊʹ�ñջ����ƻ��·ת����ת��������������Ѷȡ�

����ģ���˲�������һ��������ѶȺͽϴ�Ĺ�������������ѣ��ر��Ƕ��ڿռ���յIJ�Ʒ�����������Ա��Ը��ʹ��ģ���˲�������������һ���Ϻ����Ǽ������Ԫ�����ӱ���������������ñ������û��������͵����������Խ�Ƶ�ʺ��ɴ���ɺܴ���������һ��������;����ѡ���˲������������Դ� Maxim �ȹ�˾�������оƬ��

�����˲������������ͣ�����ʱ���˲����Ϳ��ص����˲���������ʱ���˲���ͨ����Ҫ�ⲿԪ�����ڽ�Ƶ�ʣ��Ӷ����������ǵ�����ԡ����ص����˲������Ը�����ṹ���ʹ�ã�һ������£�����������������ʱ���˲�����

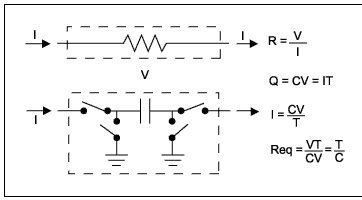

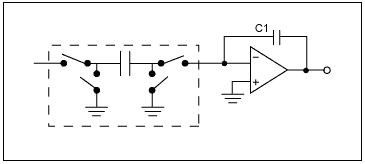

���ص����˲�����һ�ֺ���ͱ������Ͽɵ��˲����ṹ�����õ�ǰ�Ĺ蹤�ռ����ܹ��ɿ����ɡ��乤��ԭ������ѧ�Ƶ���ͼ 4 ��ʾ������ԭ���ǣ��ڵ��������˵Ŀ��ؿ����£����ݱ���硢�ŵ硣���ֵ��ת�ƹ��̲���������������Լ�����ƽ��������������Ƶ���㹻��ʱ���õ�����Ч����������ĵ������ɿ����ǵ��豻һ��������ȡ���������ͼ�ӵ���ֵȡ�����������أ����ݴ�С�Ϳ���Ƶ�ʡ�����Ƶ��Խ�ߡ�����ֵԽ�������Խ����˵������ֵԽС��������������˲����ṹ��Ƶ�����Խ����ŵ��ݳߴ��Ƶ�ʵı仯���ı䡣�ڼ��ɷ����У�����ֵ�ǹ̶��ģ��˲������ܿ���Ƶ�ʵĿ��ơ������˲�����ԭ����ͼ 5 ��ʾ��

ͼ 4. ���ص���ԭ����ͼ

ͼ 5. ���ÿ��ص��ݼ������ɼ��˲���

�˲����ľ���ȡ���ڸ���Ԫ�������ޣ����뷽���У�����ֻ��ʹ������һ�µ�Ԫ�������ڼ��ɷ����У����Ա�֤�ܸߵ�Ԫ��һ����(0.1%����)����ˣ����ǿ��Ժܺõؿ��Ƽ����˲�����Ƶ�����ԡ����磬MAX7490 �Ľ�Ƶ�ʾ��ȿ��Դﵽ 0.2%�������÷���Ԫ�������ﵽ��һָ�ꡣ���⣬���ɷ��������г�ɫ���¶����ԣ���Ưϵ�����Դﵽ 10ppm/��C��

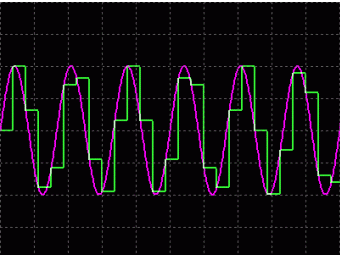

���ﻹ��Ҫ�ر�ָ�����ص��ݷ������źŵIJ���������ʱ�������ź�ת����ʱ����ɢ�źţ�����ζ�����ǻ�Ҫ�ٴο��ǻ�����⡣ֵ�����ҵ��ǣ������˲����IJ������ʷdz��ߣ�ͨ���� 100 ���Ĺ����������ԣ�ֻ�����һ���������˲�����ϵͳ������һ����Ҫ���ǵ������ǣ�����ʱ�ӵ���λ������������ʧ�棬���� ADC �д��ڵ�������ͬ��ͼ 6 ������һ����ȷ�źű����������������ᵼ��һ���ķ�����

ͼ 6. Ƿ��������ķ���ʧ��

ʱ�Ӷ��������ֱ�����ʽ�������λ���������ģ��������ͽ����ߣ���������������Եģ�ʧ��(THD)����������һ��ʱ���������磺ps ���ֵ�� RMS��Ϊ�˴ﵽһ�����źŴ��ȣ��ܹ��������Ķ�����? �ο����� 1 ��ָ��������һ�� 16 λ��ϵͳ��1nspp (���ֵ)��ʱ�Ӷ�����ʹ SNR �� 98dB ���� 91dB��Ϊ�˽�������Ӱ�����Ƶ� 0.5dB���������ܸ��� 400pspp��

�������û���ʱ���������Ժ�����������������ָ���Ҫ���磺SaRonix NTH5������ֻ�� 8psRMS (53pspp)�����ַ�����ȱ�����������ź�Ƶ�ʡ������ϵͳ�У���������(�� ADC����C����)Ҳ��Ҫ�ṩʱ�ӡ������Щʱ��������������������Щʱ�ӽ���ͬ����������������������⡣MAX7375 �� DS1085 �ܹ��������ʱ�ӣ����ұ˴�ͬ���������ṩ�ϺõĶ���ָ��(�ֱ�Ϊ 160ps �� 300ps)�����Դﵽ 90dB ���ϵ��źŴ��ȡ��������������ṩʱ�ӵ���һ���ô��ǣ��ɱ�̲�ͬ��ʱ��Ƶ�ʡ�Ҳ����˵�����Ի�þ��������ɱ��Ƶ����Ӧ���Ե�ģ���˲������Ӷ�����һ����������ϵͳ��

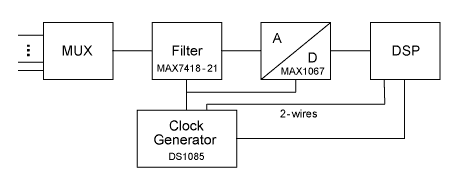

ͼ 7 �ǻ������������ṩ��һ�����ݲɼ�ϵͳ������ADC ���� 14 λ�ֱ��ʺ� 200ksps ������(MAX1067 ϵ��)��������ÿ��ת��������Ҫ 24 ��ʱ�ӡ�������˲��������� MAX7418-21 ϵ�в�Ʒ����ϵ���˲����ṩ�����˲������ͣ��籴������������˹����Բ�ȡ���Ƶ������Ϊ 1/100 fClk�����ǵ� DSP ����ת�����IJ���(ֻ��Ҫһ����ʱ��)��ͬһʱ�ӿ��������˲����� ADC����ȫͬ�������� DS1085 ����ʱ�ӣ��ܹ��õ���·ʱ�ӣ��ڶ�·ʱ�ӿ����� DSP��DS1085 ͨ�� 2 �߽ӿڱ�̣���ϵͳ�����ڲ�ͬ�IJ�������ʱ������������Ƶ�ʣ���ͬһ�� PCB ʵ�ֲ�ͬ�Ĺ��ܡ�

ͼ 7. ���ݲ���ϵͳԭ����ͼ

ͼ 7 ��ʾ��·������֮��Эͬ�������ڳɱ����ӳ̶��϶��ǿ��Խ��ܵġ�����һ�������ǿɱ���ԣ��ṩ�˼��������ԣ��ȼ�����ƣ�Ҳ�����˳ɱ���

����ϲ��

����ϲ��

��ҵ��Ѷ

��ҵ��Ѷ

ѯ��

ѯ��